Product Summary

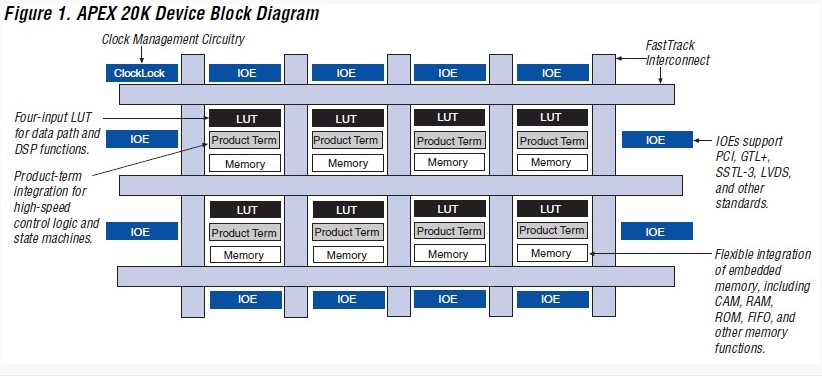

The EP20K400EFC672-1 is the first PLD designed with the MultiCore architecture, which combines the strengths of LUT-based and productterm-based devices with an enhanced memory structure. The EP20K400EFC672-1 is configured at system power-up with data stored in an Altera serial configuration device or provided by a system controller.

Parametrics

EP20K400EFC672-1 absolute maximum ratings: (1)VCCINT, Supply voltage With respect to ground: –0.5v min, 3.6 V max; (2)VCCIO: –0.5v min, 4.6 V max; (3)VI, DC input voltage: –2.0v min, 5.75 V max; (4)IOUT, DC output current, per pin: –25mA min, 25 mA max; (5)TSTG, Storage temperature: –65 to150 ℃ at No bias; (6)TAMB, Ambient temperature Under bias: –65 to 135 ℃; (7)TJ, Junction temperature:135 ℃ max at PQFP, RQFP, TQFP, and BGA packages,under bias;150 ℃ max at Ceramic PGA packages, under bias.

Features

EP20K400EFC672-1 features: (1)Industry first programmable logic device (PLD) incorporating system-on-a-programmable-chip (SOPC) integration; (2)High density; (3)Designed for low-power operation; (4)Flexible clock management circuitry with up to four phase-locked loops (PLLs); (5)Advanced interconnect structure; (6)Advanced packaging options; (7)Advanced software support.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

EP20K400EFC672-1X |

|

IC APEX 20KE FPGA 400K 672-FBGA |

Data Sheet |

|

|

||||||

|

EP20K400EFC672-1XN |

|

IC APEX 20KE FPGA 400K 672-FBGA |

Data Sheet |

|

|

||||||

(China (Mainland))

(China (Mainland))