Product Summary

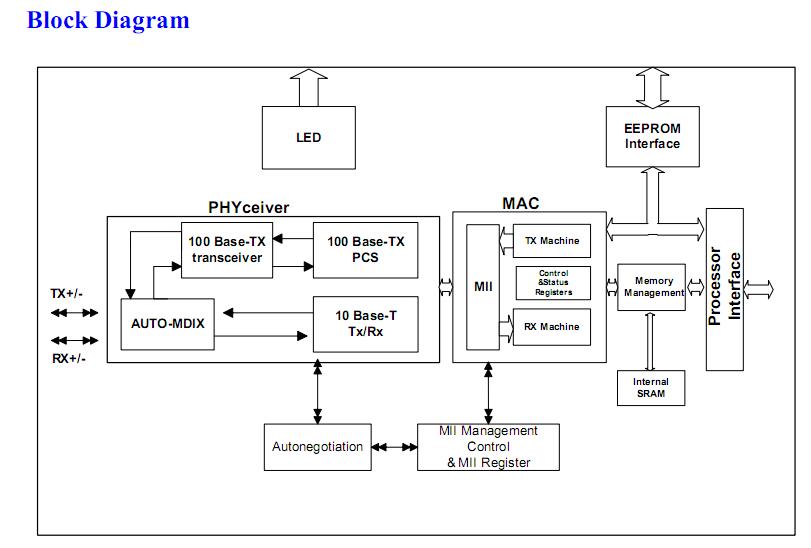

The DM9000BEP is a fully integrated and cost-effective low pin count single chip Fast Ethernet controller with a general processor interface, a 10/100M PHY and 4K Dword SRAM. It is designed with low power and high performance process interface that support 3.3V with 5V IO tolerance. The DM9000BEP supports 8-bit and 16-bit data interfaces to internal memory accesses for various processors. The PHY of the DM9000BEP can interface to the UTP3, 4, 5 in 10Base-T and UTP5 in 100Base-TX with HP Auto-MDIX. The applications of it are VoIP CPE (ATA, IP Phone, Video Phone), IP STB, IPC, Internet Radio.

Parametrics

DM9000BEP general specifications: (1)Compatible with 3.3V and 5.0V tolerant I/O; (2)DSP architecture PHY Transceiver; (3)48-pin LQFP, 0.18 um process; (4)Integrated 10/100M transceiver With HP Auto-MDIX; (5)Supports back pressure mode for half-duplex; (6)IEEE802.3x flow control for full-duplex mode; (7)Supports wakeup frame, link status change and magic packet events for remote wake up; (8)Support 100M Fiber interface; (9)Integrated 16K Byte SRAM; (10)Build in 3.3V to 1.8V regulator; (11)Supports early Transmit; (12)Supports IP/TCP/UDP checksum generation and checking ; (13)Supports automatically load vendor ID and product ID from EEPROM Optional EEPROM configuration.

Features

DM9000BEP features: (1)Network Technology: Ethernet; (2)Ethernet controller, 4k SRAM buffer, MAC, PHY; (3)Supply Range/Split & Single:+3 to +3.6V; (4)Package:LQFP48; (5)Operating Temperature Range:0 to +70℃; (6)Data Rate:10/100Mbps.

Diagrams

|

DM9000 |

Other |

|

Data Sheet |

Negotiable |

|

||||||

|

DM9000A |

Other |

|

Data Sheet |

Negotiable |

|

||||||

|

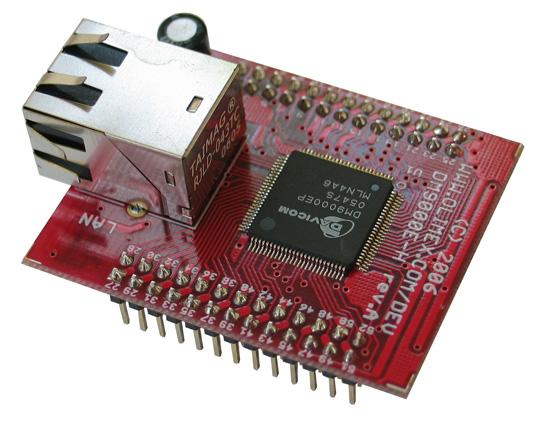

DM9000E-H |

Olimex Ltd. |

Ethernet Development Tools ETHERNET CONTROLLER HEADER BRD 50x40mm |

Data Sheet |

|

|

||||||

|

DM9000EP |

Other |

|

Data Sheet |

Negotiable |

|

||||||

|

DM9008 |

Other |

|

Data Sheet |

Negotiable |

|

||||||

|

DM9081 |

Other |

|

Data Sheet |

Negotiable |

|

||||||

(China (Mainland))

(China (Mainland))